- 您现在的位置:买卖IC网 > Sheet目录307 > ADE7569ASTZF16 (Analog Devices Inc)IC ENERGY METER MCU 16K 64LQFP

Preliminary Technical Data

OPERATING MODES

ADE7566/ADE7569

PSM0 (NORMAL MODE)

In PSM0, normal operating mode, V SW is connected to V DD . All

of the analog and digital circuitry powered by V INTD and V INTA

are enabled by default. In normal mode, the default clock

frequency, f CORE , established during a power-on reset or software

reset, is 1.024 MHz.

?

?

The RAM in the MCU is no longer valid.

The program counter for the 8052, also held in volatile

memory, becomes invalid when the 2.5 V supply is shut

down. Therefore, the program does not resume from

where it left off, but always starts from the power-on reset

vector when the ADE7566/ADE7569 come out of PSM2.

PSM1 (BATTERY MODE)

In PSM1, battery mode, V SW is connected to V BAT . In this operating

mode, the 8052 core and all of the digital circuitry are enabled

by default. The analog circuitry for the ADE energy metering

DSP powered by V INTA is disabled. This analog circuitry auto-

matically restarts once the V DD supply is above 2.75 V and if

the PWRDN bit in the MODE1 Register (0x0B) is cleared.

The default f CORE for PSM1, established during a power-on

reset or software reset, is 1.024 MHz.

PSM2 (SLEEP MODE)

PSM2 is a low power consumption sleep mode for use in battery

operation. In this mode, VSW is connected to VBAT. All of the

2.5 V digital and analog circuitry powered through V INTA and V INTD

are disabled, including the MCU core, resulting in the

following:

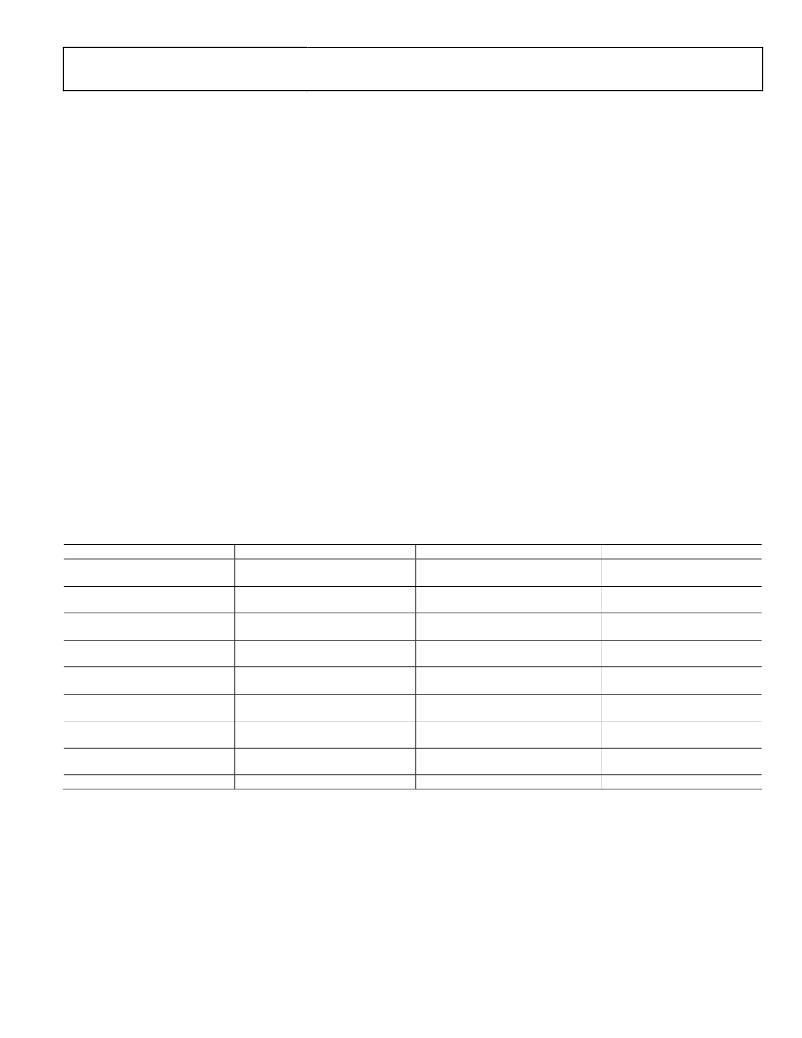

Table 25. SFR Maintained in PSM2

The 3.3 V peripherals (temperature ADC, VDCIN ADC, RTC,

and LCD) are active in PSM2. They can be enabled or disabled

to reduce power consumption and are configured for PSM2

operation when the MCU core is active (see Table 26 for more

information about the individual peripherals and their PSM2

configuration). The ADE7566/ADE7569 remain in PSM2 until

an event occurs to wake it up.

In PSM2, the ADE7566/ADE7569 provide four scratch pad

RAM SFRs that are maintained during this mode. These SFRs

can be used to save data from PSM0 or PSM1 when entering

PSM2 (see Table 18 to Table 22).

In PSM2, the ADE7566/ADE7569 maintain some SFRs (see

Table 25). The SFRs that are not listed in this table should be

restored when the part enters PSM0 or PSM1 from PSM2.

I/O Configuration

Interrupt Pins Configuration SFR

(INTPR, 0xFF)

Peripheral Configuration SFR

(PERIPH, 0xF4)

Port 0 Weak Pull-Up Enable SFR

(PINMAP0, 0xB2)

Port 1 Weak Pull-Up Enable SFR

(PINMAP1, 0xB3)

Port 2 Weak Pull-Up Enable SFR

(PINMAP2, 0xB4)

Scratch Pad 1 SFR (SCRATCH1, 0xFB)

Power Supply Monitoring

Battery Detection Threshold SFR

(BATVTH, 0xFA)

Battery Switchover Configuration SFR

(BATPR, 0xF5)

Battery ADC Value SFR (BATADC, 0xDF)

Peripheral ADC Strobe Period SFR

(STRBPER, 0xF9)

Temperature and Supply Delta SFR

(DIFFPROG, 0xF3)

VDCIN ADC Value SFR (VDCINADC, 0xEF)

RTC Peripherals

RTC Nominal Compensation SFR

(RTCCOMP, 0xF6)

RTC Temperature Compensation SFR

(TEMPCAL, 0xF7)

RTC Configuration SFR (TIMECON, 0xA1)

Hundredths of a Second Counter SFR

(HTHSEC, 0xA2)

Seconds Counter SFR (SEC, 0xA3)

Minutes Counter SFR (MIN, 0xA4)

LCD Peripherals

LCD Segment Enable 2 SFR

(LCDSEGE2, 0xED)

LCD Configuration Y SFR

(LCDCONY, 0xB1)

LCD Configuration X SFR

(LCDCONX, 0x9C)

LCD Configuration SFR (LCDCON,

0x95)

LCD Clock SFR (LCDCLK, 0x96)

LCD Segment Enable SFR

(LCDSEGE, 0x97)

Scratch Pad 2 SFR (SCRATCH2, 0xFC)

Temperature ADC Value SFR

Hours Counter SFR (HOUR, 0xA5)

LCD Pointer SFR (LCDPTR, 0xAC)

(TEMPADC, 0xD7)

Scratch Pad 3 SFR (SCRATCH3, 0xFD)

Scratch Pad 4 SFR (SCRATCH4, 0xFE)

–

–

Alarm Interval SFR (INTVAL, 0xA6)

–

LCD Data SFR (LCDDAT, 0xAE)

–

Rev. PrA | Page 31 of 136

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADE7752BARWZ-RL

IC ENERGY METERING 3PHASE 24SOIC

ADE7755ARSZ

IC ENERGY METERING 1PHASE 24SSOP

ADE7757ARNZRL

IC ENERGY METERING 1PHASE 16SOIC

ADE7758ARWZRL

IC ENERGY METERING 3PHASE 24SOIC

ADE7761AARSZ-RL

IC ENERGY METERING 1PHASE 20SSOP

ADE7761BARSZ-RL

IC ENERGY METERING 1PHASE 20SSOP

ADE7768ARZ-RL

IC ENERGY METERING 1PHASE 16SOIC

ADE7769ARZ-RL

IC ENERGY METERING 1PHASE 16SOIC

相关代理商/技术参数

ADE7569ASTZF162

制造商:AD 制造商全称:Analog Devices 功能描述:Single-Phase Energy Measurement IC with 8052 MCU, RTC, and LCD Driver

ADE7569ASTZF16-RL

功能描述:IC ENERGY METER 1PHASE 64-LQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 能量测量 系列:- 产品培训模块:Lead (SnPb) Finish for COTS

Obsolescence Mitigation Program 标准包装:2,500 系列:*

ADE7569ASTZF16-RL2

制造商:AD 制造商全称:Analog Devices 功能描述:Single-Phase Energy Measurement IC with 8052 MCU, RTC, and LCD Driver

ADE7751

制造商:AD 制造商全称:Analog Devices 功能描述:Energy Metering IC with On-Chip Fault Detection

ADE7751AAN-REF

制造商:AD 制造商全称:Analog Devices 功能描述:Energy Metering IC with On-Chip Fault Detection

ADE7751AN

制造商:Analog Devices 功能描述:Energy Measurement 24-Pin PDIP 制造商:Analog Devices 功能描述:ENERGY MEASUREMENT 24PDIP - Bulk 制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONVERTER I.C. - Bulk

ADE7751ARS

制造商:Rochester Electronics LLC 功能描述:PRODUCT TO FREQUENCY CONVERTER I.C. - Bulk 制造商:Analog Devices 功能描述:IC ENERGY METER

ADE7751ARSRL

制造商:Analog Devices 功能描述:Energy Measurement 24-Pin SSOP T/R 制造商:Analog Devices 功能描述:IC ENERGY METER